石英晶体

石英(SiO2)由硅和氧两种元素组成。

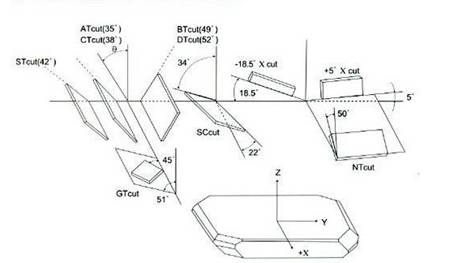

切割角度和振动模式

根据不同用途,将石英晶棒按照特定的晶向切割成晶片,即可制成石英晶体。其振动切型、频率变化及其特性如图所示:

标称频率

该频率特指晶体元器件的性能指标,表示为MHz或KHz。

频率偏差

标称频率在一定温度(一般是25℃)下的允许偏差,表示为百分数(%)或百万分之几(ppm)。

频率稳定性

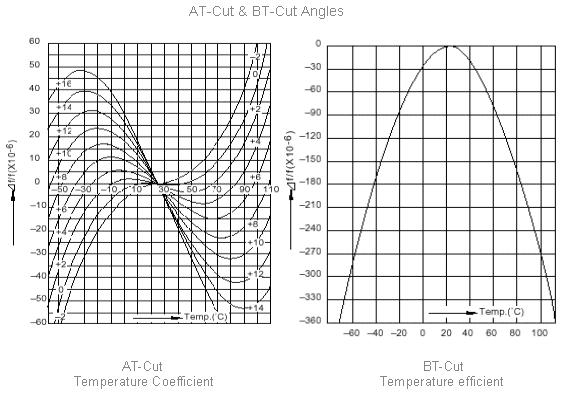

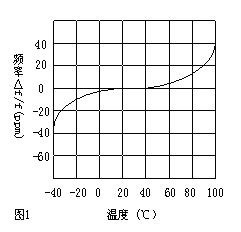

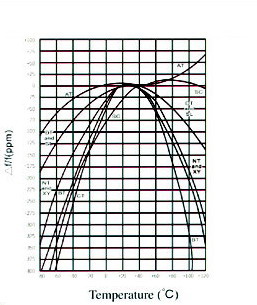

稳定性是指标称频率在一定温度范围内的允许偏差,规定在25℃下,此项偏差为0,以标称频率的百分数(%)或百万分之几(ppm)来表示。如前所述,这个参数与石英晶片的切角密切相关。

频率温度特性:

AT切厚度切石英晶体随切角变化的频率温度特性曲线。由于AT切频率温度特性等效于三次方程,因此在较宽的温度范围内有较好的频率稳定性。

工作温度范围

石英晶体元器件在规定的误差内工作的温度范围。

储存温度范围

晶体在非工作状态下保持标准特性的温度范围。

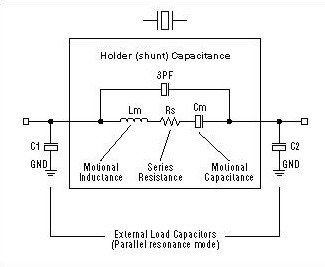

等效电路

一个产生主谐振频率的石英晶体可以表达为一个等效电路---一般包括一个由电感、电容和电阻组成的串联电路和一个与这个串联电路并联的电容,如图所示。

在这里,C0为是静态电容,包括电极间的静态电容和端子间的杂散电容。

将石英晶体元器件视为一个电子和机械的振动系统时,L1和C1就是它的等效常数。由于这两个常数取决于切型、切角、晶片尺寸和电极结构等因素,并且可以反复调整,故而石英晶体元器件的精度可以做得很高。

R1表示振荡损耗,受切割方式、装联方式、晶片形状和晶片尺寸的控制。

负载电容(CL)

任何外部电容一旦与石英晶体元器件串联,即会成为其谐振频率一个决定因素。负载电容变化时,频率也会随之改变。因此,在电路中使用时,经常会以标准负载电容来微调频率至期望值。

静态电容(C0)

电极之间的静态电容和安装系统中的杂散电容。

等效串联电阻(ESR,Rr,R1)

晶体在谐振频率下的电阻值,ESR表示晶体的阻抗,单位为欧姆。

激励电平

流过晶体的激励电流的一项功能。激励电平是晶体中功率损耗的数值。最大功率是大多数功率器件在保证正常电气参数的情况下,维持工作所消耗的功率,单位为mW或uW。激励电平应维持在确保石英晶体正常起振和稳定振荡所需要的最低值,以避免年老化特性不良和晶体损伤。

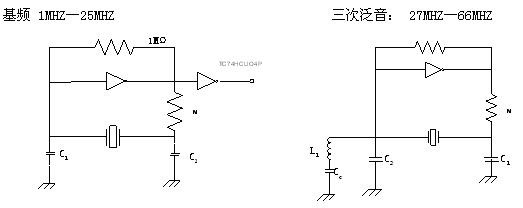

泛音晶体

晶体通常在基频下工作,但对电路做轻微调整后,即可在第三、第五、第七、第九倍频下工作。为了保证泛音晶体在特定的倍频下振动,其切型角度、平行度和表面光洁度经过了特殊修正。

绝缘电阻

引线之间或引线和壳体之间的电阻。

品质因素

“Q”值是晶体等效电路中动态臂谐振时的品质因素。振荡电路所能获得的最大稳定性直接与电路中晶体的Q值相关。Q值越高,晶体带宽(“F”)越小,电抗值(fs-fa)变化越陡,外部电抗对晶体的影响越小。

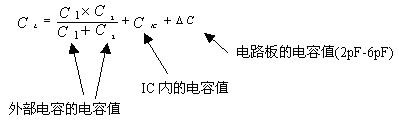

CL=(C1×C2)/(C1+C2)+杂散电容 杂散电容可以在2pF-6pF之间变化

注意

寄生

所有石英谐振器均有寄生(在主频率之外的不期望出现的)振荡响应。他们在等效电路图中表现为附加的以R1、L1、C1形成的响应回路。寄生响应的阻抗RNW与主谐振波的阻抗Rr的比例通常以衰减常数dB来表示,并被定义为寄生衰减

aNW=-20·lg

对于振荡用晶体,3至6dB是完全足够的.对于滤波用晶体,通常的要求是超过40dB. 这一规格要求只有通过特殊设计工艺并使用数值非常小的动态电容方能达到.可达到的衰减随着频率的上升和泛音次数的增加而减小. 通常的平面石英晶片谐振器比平凸或双面凸晶片谐振器的寄生衰减要良好. 在确定寄生响应参数时,应同时确定一个可接受的寄生衰减水平以及寄生频率与主振频率的相对关系.

在AT切型中,对于平面晶片,"不和谐的响应"只存在于主响应的+40至+150KHZ之间,对于平凸或双面凸的晶片,寄生则在+200至+400KHZ之间.在以上的测量方法中,寄生响应衰减至20至30dB时是可以测量的,对于再高一些的衰减.C0的补偿是必需的.

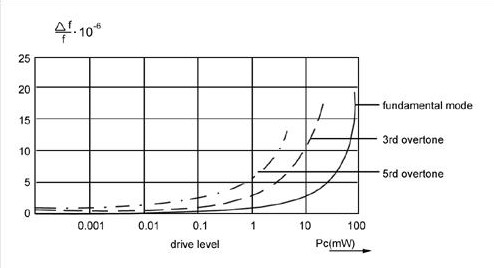

激励功率依赖性

石英振荡器的机械振动的振幅会随着电流的振幅成正比例地上升.功率与响应阻抗的关系为Pc=12qR1, 高激励功率会导致共振的破坏或蒸镀电极的蒸发,最高允许的功率不应超过10mV.

由于L1和C1电抗性的功率振荡,存在Qc=Q x Pc. 若Pc=1mV, Q=100.000, Qc则相当于100W.由于低的Pc功率会导致振荡幅度的超过,最终导致晶体的频率上移.

随着晶体泛音次数的增加,对于激励功率的依赖性更加显著.上图显示了典型的结果,但是精确的预期结果还是要受到包括晶体设计和加工,机械性晶片参数,电极大小,点胶情况等的影响.

可以看出,激励功率必须被谨慎地确定,以使晶体在生产中和使用中保持良好的关系.

当今,一个半导体振荡回路的激励功率一般为0.1mV,故在生产晶体时也一般按0.1mV进行.

一个品质良好的晶体可以容易地起振,其频率在自1nW逐步增加时均能保持稳定.现在,晶体两端的功率很低的半导体回路也可以在很低的功率的情况下工作良好.

上图显示了一个对激励功率有或无依赖性的晶体的工作曲线的比较.

晶体存在蒸镀电极不良,晶片表面洁净度不足,都会存在如图所示的在低功率时出现高阻抗的情况,这一影响称为激励功率依赖性(DLD).通常生产中测试DLD是用1~10mV测试后再用1mV测试,发生的阻抗变化可作为测试的标准.很显然,在增加测试内容会相当大的提高晶体生产的成本.

利用适当的测试仪器可以很快地进行DLD极限值的测定,但是只能进行合格/不合格的测试.IEC草案248覆盖了根据(DIV)IEC444-6制定的激励功率的依赖性的测量方法.

提供具有充分的反馈和良好脉冲的最优化的振荡回路,可以极大的消除振荡的内部问题.

老化

工作频率在特定时间范围内的变化量,一般表达为最大值,单位是每年频率变化量的百万分之几(ppm/年)。频率随时间而变化的原因有很多,如:密封特性和完整性、制造工艺、材料类型、工作温度和频率。

常用计算公式:

|

计算公式 |

定义 |

|

fS = (Series) frequency = |

C0 = Static Capacitance in farads |

|

CL = Load capacitance = |

C1 = Motional capacitance in farads |

|

Co = Shunt capacitance = |

CL = Load capacitance in farads |

|

C1 = Motional capacitance = |

f = Nominal frequency in Hz |

|

L1 = Motional inductance = |

fL = Anti-resonant frequency in Hz |

|

R1 = Series resistance = |

fS = Series resonant frequency in Hz |

|

Q = Quality factor = |

L = Inductance into Henrys |

|

fL - fS = f = |

PL = Pullability (ppm/pF) |

|

PL = Pullability = |

Q = Quality factor |

|

|

R1 = Series resistance in ohms |